Read Level 介绍

Vth 基本原理

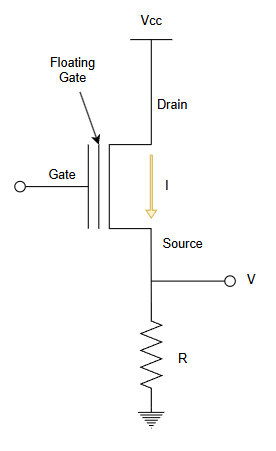

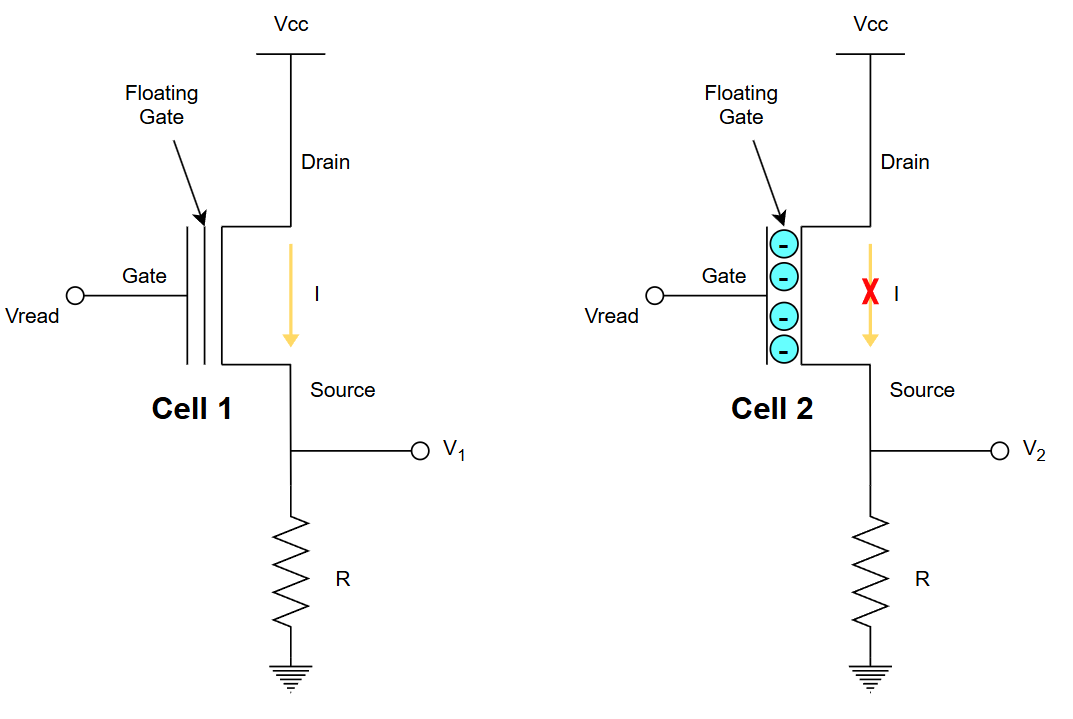

上图是 Nand Flash 最基础的存储单元,该单元被称为 1 个 Cell。每个 Cell 均由 1 个 FGMOS(浮栅型金属 - 氧化物 - 半导体场效应晶体管,即 Floating-gate MOSFET)构成 —— 相比普通 MOSFET,它额外增加了一层 “浮栅(Floating Gate)” 结构。

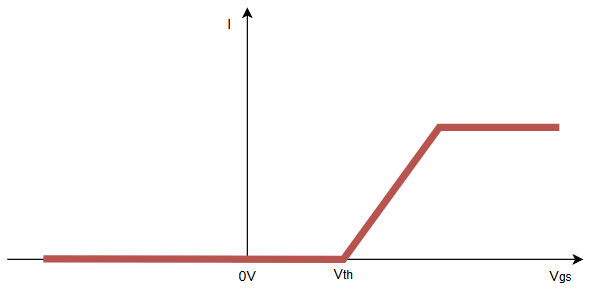

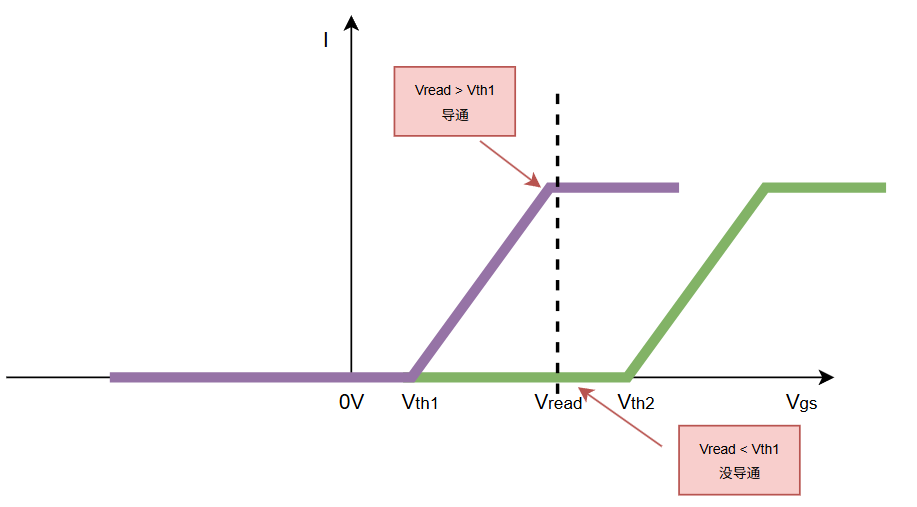

可将 MOSFET 理解为 1 个可受控调节的电阻:当在其栅极(Gate)与源极(Source)之间施加电压Vgs时,会改变漏极(Drain)与源极(Source)之间的电流I,进而间接改变此处的电压V(即需测量的目标电压),其 I-V 特性曲线下图所示。

- 当栅源电压Vgs小于导通电压Vth时,漏源电流I始终为 0,Cell 处于不导通状态,此时测量得到的漏源电压V等于 0。

- 当Vgs大于Vth时,Cell 开始导通,漏源电流I随Vgs增大而逐渐上升,漏源电压V也随之增大。

- 其中,Vth被定义为 “导通电压”。该电压值越高,意味着 Cell 需要更大的Vgs才能启动导通,整体导通难度也随之增加。

Vth 调控原理

浮栅(Floating Gate)是 FGMOS 的核心结构,其核心功能是存储电子,并通过电子存储量的变化直接调控 Cell 的导通电压Vth,最终实现数据的物理存储。

电子存储原理:量子隧穿效应

浮栅的电子存储依赖量子隧穿效应(Tunneling Effect) ,具体机制与关键特性如下:

- 效应本质:在特定电场条件下(如栅极施加高电压),电子可突破氧化层的能量壁垒,“隧穿” 进入浮栅并被束缚其中,实现电子存储;反向电场则可使电子从浮栅隧穿流出,完成擦除。

- 关键特性:隧穿效应的发生具有概率性,并非施加电压后所有电子都会立即隧穿。该特性会直接影响后续 VT 分布图的形态,例如导致曲线出现一定宽度的分布而非绝对尖锐的峰值。

电子存储对 Vth 的影响机制

浮栅中电子的有无,会通过 “内建偏压” 改变 Vth,具体逻辑可通过公式与实例说明:

核心公式关联:当浮栅存储电子时,相当于在栅极(Gate)与源极(Source)之间额外叠加了一个负向内建偏压 Vfb。此时,实际作用于沟道的有效栅源电压变为:

Vgs (eff) = Vgs (外施) - Vfb

为使 Cell 导通(Vgs (eff) ≥ Vth (初始)),需更高的外施 Vgs,即等效表现为Vth 增大。

实例对比(基于读操作 Vread):

存储状态 浮栅电子 Vth 大小 施加相同 Vread 时的状态 读出电压 V Cell 1(数据 “0”) 无 较小(Vth1) Vread ≥ Vth1,Cell 导通 V1 ≠ 0(有电流对应电压) Cell 2(数据 “1”) 有 较大(Vth2) Vread < Vth2,Cell 截止 V2 = 0(无电流)

电压与功能对应

| 操作类型 | 操作名称 | 所需电压(概略值) | 核心作用 | 对 Cell 状态的影响 |

|---|---|---|---|---|

| Program | 编程(写) | +20V(正向高压 Vprog) | 将电子 “注入” 浮栅 | 浮栅电子增多 → Vth(导通电压)增大 |

| Erase | 擦除 | -20V(负向高压 Verase) | 将电子从浮栅 “抽出” | 浮栅电子减少 → Vth(导通电压)减小 |

| Read | 读取 | 0~10V(低压) | 检测 Cell 导通状态以判断数据 | 不改变浮栅电子数量,无状态损耗 |

Read Level

上面讲到的Cell只有 “1” 和 “0” 两种状态,仅需 1 个阈值电压就能区分 2 种状态,这种存储方式叫做SLC(单层单元, Single-Level Cell)

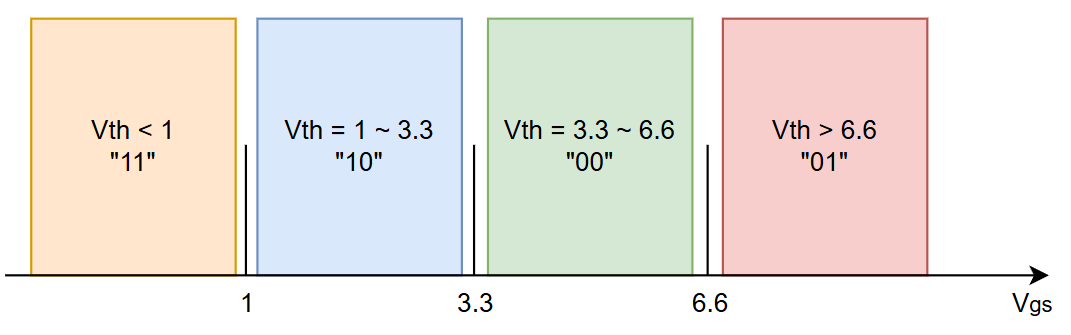

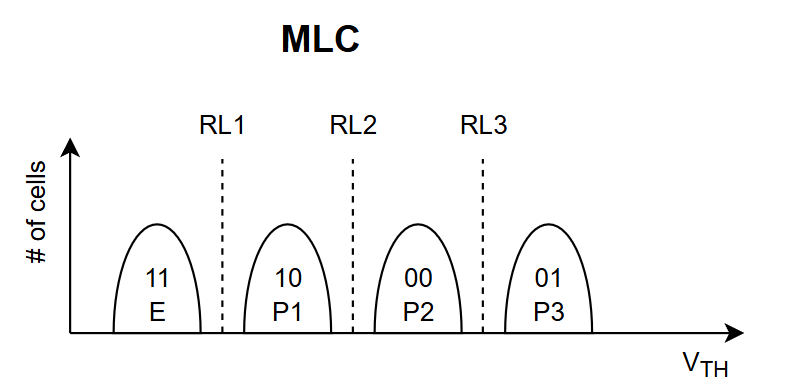

随着技术对导通电压Vth的控制精度提升,Nand Flash 实现了MLC(多层单元,Multi-Level Cell) 存储方案 —— 单个 Cell 可存储 2 个 bit 的数据,核心原理是通过设置多个Read Level(读取电平) ,区分 Cell 中不同的 Vth 区间,进而对应不同的二进制信息。

当前主流 Nand Flash 普遍采用TLC(三层单元,Tri-Level Cell) 和QLC(四层单元,Quad-Level Cell) 方案,分别实现单个 Cell 存储 3bit 和 4bit 数据。二者核心原理与 MLC 一致,均通过细分 Vth 区间和增加 Read Level 数量实现,仅在区间划分精度和电平数量上进一步提升。

| 单元类型 | 单 Cell 存储 bit 数 | Vth 区间数量(2^n) | 所需 Read Level 数量 | 核心逻辑差异 |

|---|---|---|---|---|

| MLC | 2bit | 4 个 | 3 个(区分 4 个区间) | 基础区间划分,Read Level 数量较少 |

| TLC | 3bit | 8 个 | 7 个(区分 8 个区间) | Vth 区间更细,对控制精度要求更高 |

| QLC | 4bit | 16 个 | 15 个(区分 16 个区间) | Vth 区间最细,Read Level 数量最多,需更高校准精度 |

举个MLC例子:

只需按顺序向其施加 1V、3.3V、6.6V 这三个不同的Vread(读取电压),并记录 Cell 在哪个电压下首次导通,即可反向判断其存储的具体数据;这些用于区分 Vth 区间的特定 Vread,统称为Read Level(读取电平)