Nand Vth 阈值分布

Vth 分布

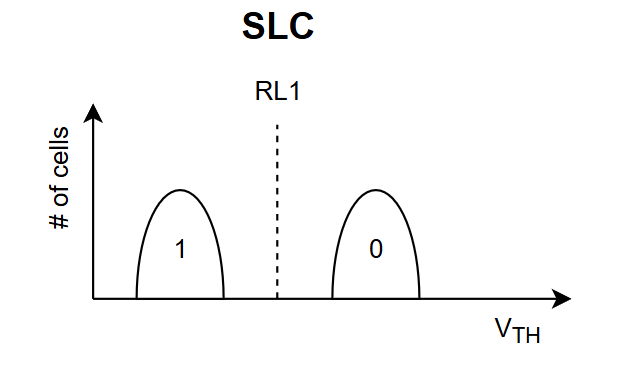

SLC(Single-Level Cell,单级单元)存储架构中,单个存储单元(Cell)仅能存储 1 个 bit 的数据,这一特性决定了它仅需两种工作状态即可实现数据表征 —— 分别为 “擦除态(Erased)” 与 “编程态(Programmed)”。

在电压阈值(Vth)分布层面,两种工作状态对应呈现出两个独立且清晰的分布峰。基于这一特性,数据读取过程无需复杂的电压判断逻辑:只需设置一个读取电压(Vread,标记为 RL1),并将其精准置于两个 Vth 分布峰的中间区间。如此一来,通过检测字线(WL)下所有存储单元的实际 Vth 值与 RL1 的相对大小,即可快速区分单元处于 “擦除态” 还是 “编程态”,进而准确读出对应 1 个 bit 的数据。

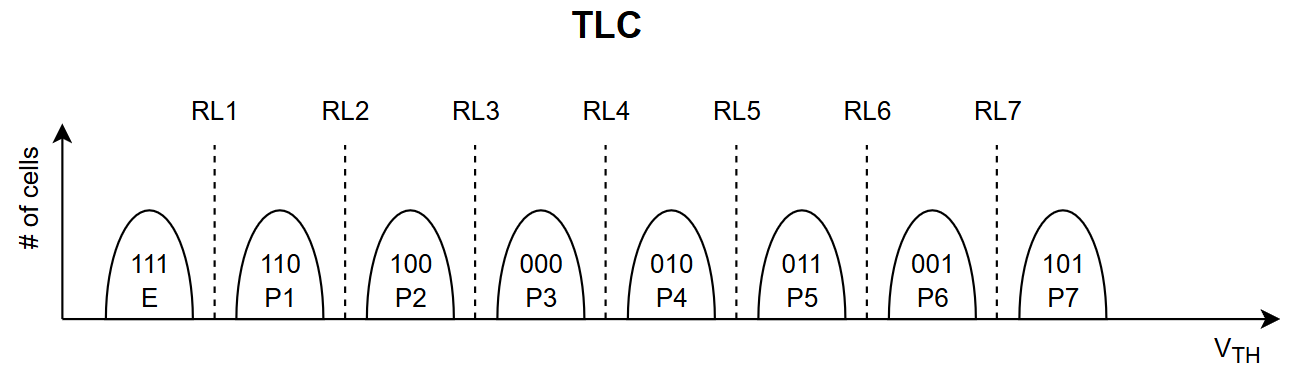

TLC(Triple-Level Cell,三级单元)存储架构通过更精细的电压控制,实现了单个存储单元存储 3 个 bit 数据的突破,而 3 个 bit 的数据组合共可形成 8 种不同的逻辑状态,具体对应为:111、110、100、000、010、011、001、101。

从Vth分布来看,这 8 种逻辑状态各自对应独立的电压区间,最终呈现为8 个明显的 Vth 分布峰(每个逻辑状态对应唯一的 Vth 分布峰)。相较于 SLC,TLC 的 Vth 分布峰数量大幅增加且峰间间距更精细,这对读取电压的设置精度、数据区分逻辑复杂度提出了更高要求 —— 需通过多组独立读取电压依次检测,才能准确识别每个存储单元所属的 Vth 分布峰,进而完整解析出 3 个 bit 的数据。

正态分布

NAND 闪存阈值电压(Vt)呈正态分布,核心是制造与工作中无法避免的 “随机性扰动因素”—— 存储单元内的随机杂质与结构不完美性,导致电子移动行为具统计随机性,大量单元 Vth 数据聚合后符合正态分布。

具体来看,半导体制造中,沟道、电荷捕获层残留的随机杂质(如金属离子、晶格缺陷),会形成 “电势陷阱” 或 “导电阻碍”,使不同单元电子移动阻力有差异,Vt 值高低不同;器件结构不完美(如氧化层厚度波动、电极界面粗糙)进一步放大随机性,比如氧化层薄则电子隧穿易、Vt 低,厚则隧穿难、Vt 高。

因杂质分布、结构差异是随机事件,且单个 NAND 芯片含数百万至上亿个单元,依据中心极限定理,大量独立随机变量(各单元 Vth 值)的统计结果会趋近正态分布,表现为 “钟形” 曲线,多数单元 Vth 集中在均值附近,少数因极端情况处于两端。

阈值电压

简单类比:把 NAND 存储单元想象成一个 “电子开关”,而阈值电压就是让这个开关刚好 “导通” 或 “断开” 的临界电压值—— 它是判断存储单元状态、实现数据读写的核心基准。

阈值电压的核心作用:定义逻辑状态

阈值电压本质是区分单元 “0” 和 “1” 逻辑状态的电压界限,随存储类型(如 SLC、TLC)调整:

电压低于 Vt,单元 “断开”(如对应逻辑 “0”);电压高于 Vt,单元 “导通”(如对应逻辑 “1”)。

SLC 仅需 1 个阈值电压就能区分 2 种状态,TLC 因需区分 8 种状态,会设多组 Vth 区间,核心仍是通过 “电压是否超阈值” 判断状态。

需要注意的是,前文提到的 SLC 仅需 1 个阈值电压就能区分 2 种状态,而 TLC 因需区分 8 种状态,会对应设置多组不同的阈值电压区间,本质仍是通过 “电压是否超过某一阈值” 来判断单元的具体逻辑状态。

阈值电压对数据读写的关键影响

阈值电压的大小和稳定性,直接决定了 NAND 闪存数据读写的准确性和可靠性:

读取环节:若阈值电压设置不合理(如过于靠近某一 Vth 分布峰),可能导致误判单元逻辑状态;

编程 / 擦除环节:每次写入或擦除数据,本质是通过调整单元内的电荷量来改变其实际 Vth 值 —— 若阈值电压漂移(如因长期使用出现电荷泄漏),会导致单元难以稳定维持目标逻辑状态,进而影响数据存储寿命;

与 Vth 分布的关联:Vt 正态分布是大量单元实际 Vth 的统计结果,标准 Vth 需避开分布峰边缘以确保识别准确。

TLC Vth 分布

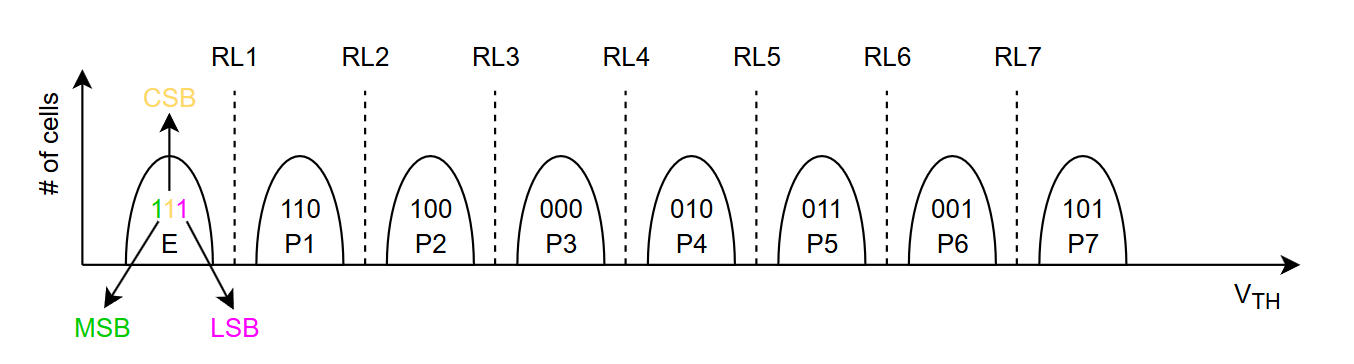

前文已提及,TLC 单个 Cell 存储 3 个 bit 时,3 个 bit 的二进制组合共形成 8 种逻辑状态(111、110、100、000、010、011、001、101)。而图中呈现的 8 个 Vth 峰,正是这 8 种逻辑状态在 “电压阈值维度” 的直观体现

每个 Vth 峰对应的 3 个 bit 并非随机组合,而是按 “位权重” 分为最高有效位(MSB,Most Significant Bit)、中间有效位(CSB,Central Significant Bit)、最低有效位(LSB,Least Significant Bit) ,三者共同定义峰的逻辑状态。(下面举例格雷码2-3-2的Vth 分布)

图中最左侧为 Erased(擦除)状态对应的 Vth 峰,且存在明确的 bit 差异规律:

相邻峰(如 P1 与 P2、P3 与 P4、P5 与 P6)之间仅存在 1 个 bit 值不同,具体表现为仅 CSB(中间有效位)的取值有差异;

这种 “相邻峰仅 1 个 bit 不同” 的设计,本质是采用了 Gray Code(格雷码)编码方式,可减少数据读写时的误判概率。

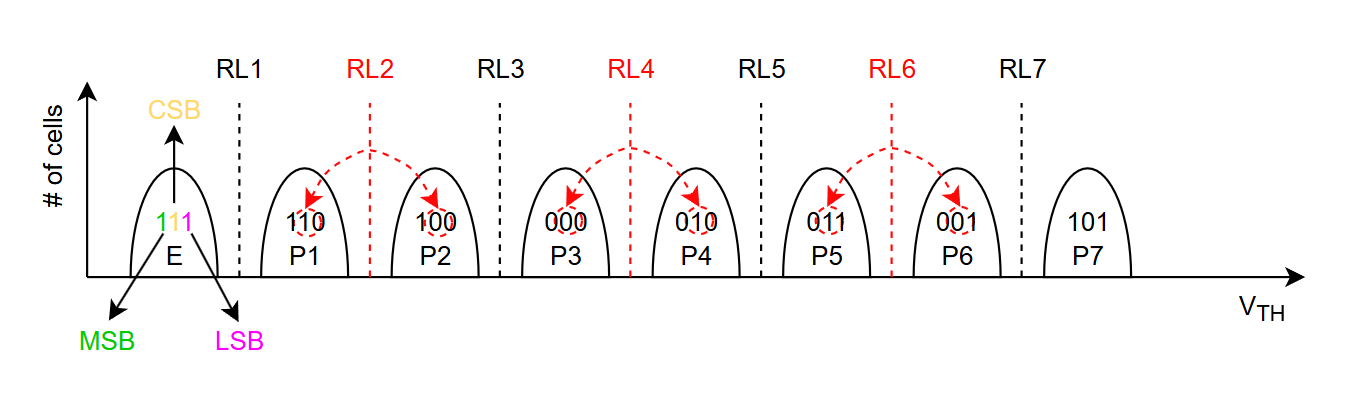

上图可以分析,想要识别CSB的bit值,需要第一次在RL6读,第二次在RL4读,第三次在RL2读一下,通过三次reference的read,做一次异或运算得到最终的bit值。

TLC 的三个 bit(LP、UP、XP)或者(LSB、CSB、MSB)对应 TLC page,读取 8 种 Vth 分布状态需按特定规则操作:LP 读 2 次(用 RL5、RL1),UP 读 3 次(用 RL6、RL4、RL2),XP 读 2 次(用 RL7、RL3)。

这仅仅是一种TLC分布,常有的TLC Gray Code:2-3-2、1-2-4、1-3-3。

不同存储介质因 “存储单元状态数” “读写机制” “可靠性需求” 不同,会采用适配的格雷码方案,而格雷码的差异会直接影响读写速度、数据可靠性、错误校正复杂度、功耗四大核心指标。