Nand Training

Nand Training Feature

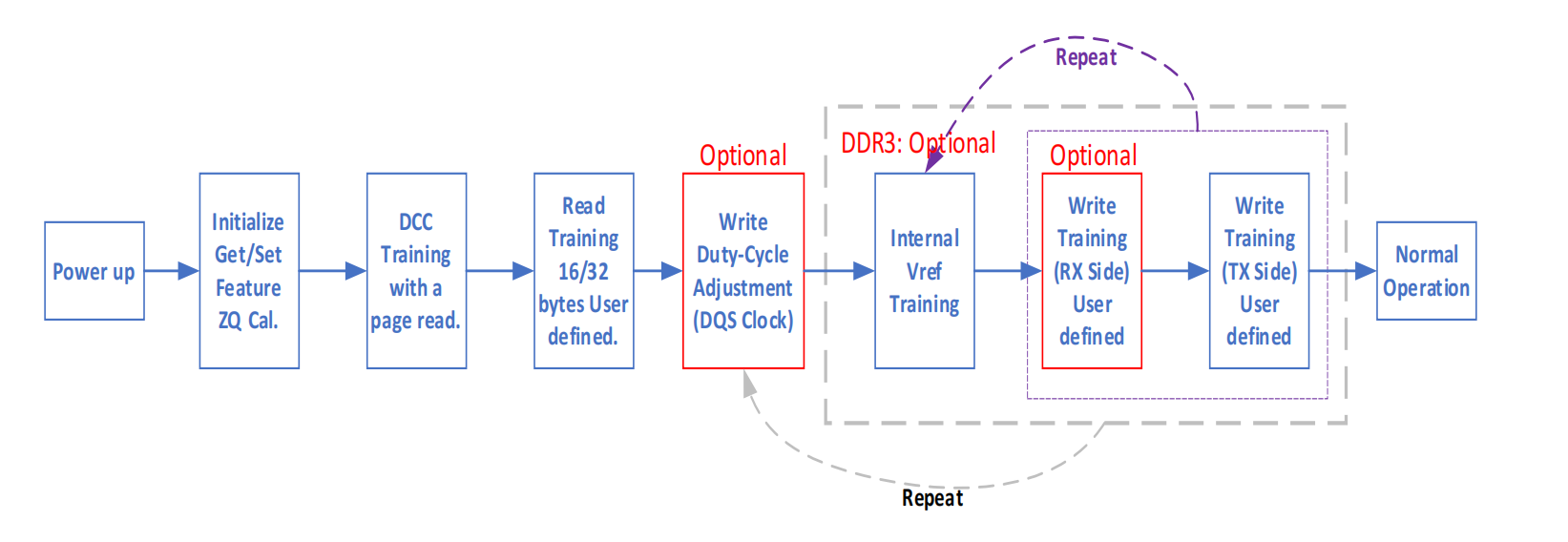

Training features shown in this section shall be supported by NAND devices operating over 800MT/s in heavily loaded systems.

Nand Training Type

- ZQ Calibration

- DCC Training

- Read DQ Training

- Write DQ Training

- WDCA(Option)

- Internal VrefQ

ZQ Calibration

ZQ Calibration 介绍

ZQ Calibration是一种电子调整过程,用于精确设定芯片输入/输出接口的电阻值,以确保在高速数据传输中信号清晰稳定,减少错误。ZQ Calibration就是这个“调音师”,它使用一个外部精密参考电阻作为“标准音叉”,来校准芯片内部电路这个“乐器”的音准(电阻值),无论环境如何变化,都能保持最佳性能。

ZQ Calibration的作用:它是一个动态、持续的过程。内存控制器会在初始化、退出低功耗状态、或者定期发起ZQ Calibration命令,让内存芯片根据当前的实时温度和电压重新进行校准,确保从轻载到重载的全工况下都能保持最佳状态。

核心功能:

- 动态阻抗匹配

- 补偿环境温度

- 提升系统稳定性

- 支持高频与高带宽

- 降低功耗

- 自动化与兼容性

Nand端 ZQ Calibration

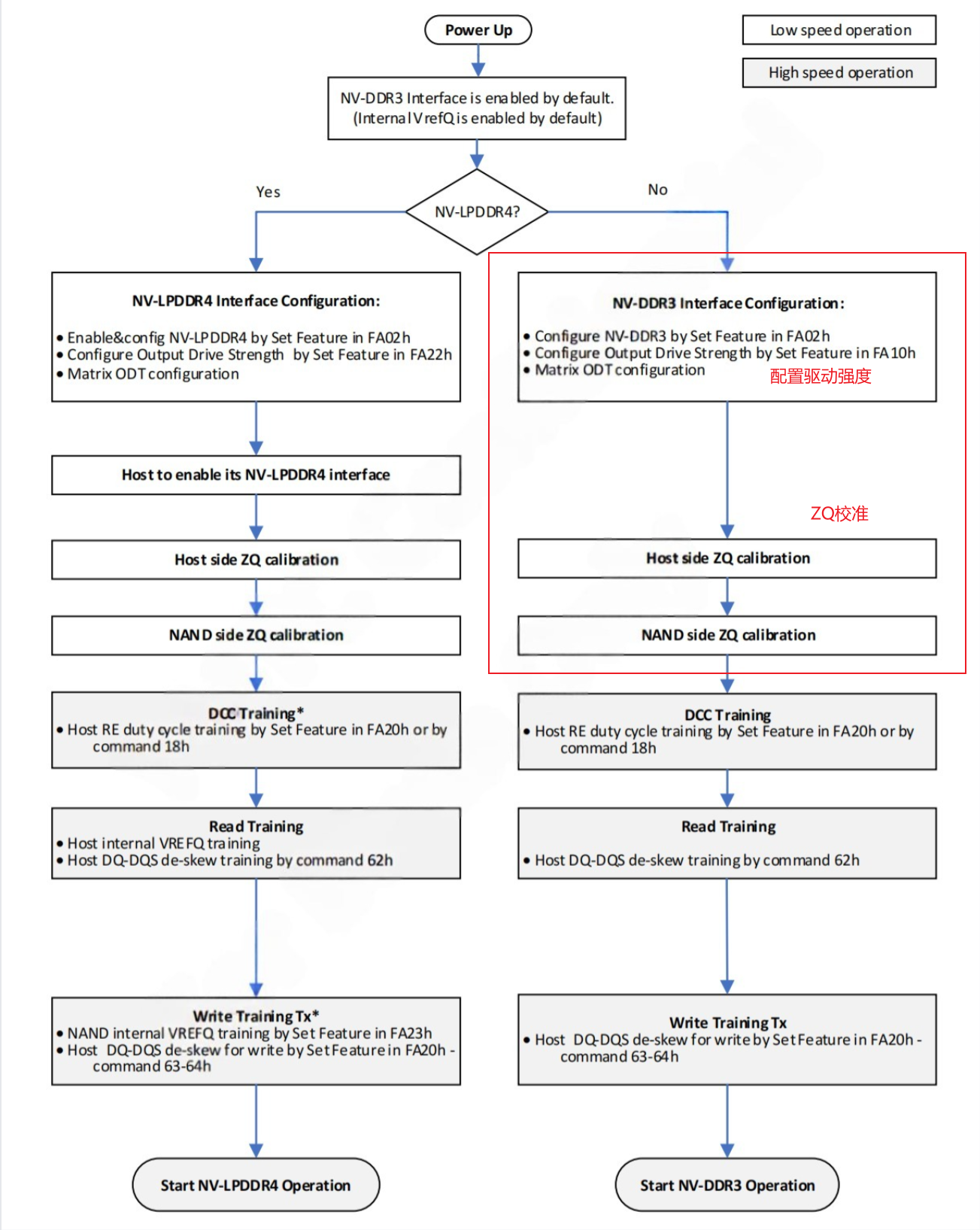

- 对于超过400MT/s速度的NV-DDR3接口,ZQ校准是可选的,但推荐使用。

- 对于NV-LPDDR4接口,无论数据速率如何,都需要进行ZQ校准。

ZQ Calibration分为长校准和短校准。

两者区别如下:

| 特性 | 长校准 | 短校准 |

|---|---|---|

| 主要目的 | 全面、精确的校准,建立初始基准或应对重大环境变化 | 快速、局部的微调,跟踪和补偿微小的漂移 |

| 触发时机 | 1. 上电初始化(Power-On) 2. 退出自刷新模式(Exit Self-Refresh) 3. 温度发生剧烈变化后(由传感器检测) 4. 可能由软件手动触发 |

在正常激活状态(Active状态) 下,由内存控制器定期发起 |

| 校准时长 | 较长 tZQCL(通常是时钟周期的数百倍,可以通过看RB拉低时间) | 非常短 tZQCS(通常比长校准短一个数量级) |

| 功耗影响 | 相对较高,因为需要启动完整的校准电路并持续较长时间 | 非常低,因为只是对当前设置进行小幅修正 |

注意事项:

- 在tZQCL或tZQCS期间,控制器不得对NAND通道(即数据总线)执行任何操作,包括读取状态。

- 如果需要使用ZQ校准时,需要注意主控端应当同步进行ZQ校准。

- 目前大多数切高速的流程中加了ZQ校准流程(ZQ长校准),但是实际高速运行过程中,是否需要加入定时的ZQ短校准,可以根据实际情况提出方案(一般不考虑)。

- 如果需要使用ZQ短校准,应该需要注意时间间隔。

- ZQ校准时,需要将DQ配置为High阻抗。

ZQ Calibration和驱动强度的关系

驱动强度好比音响的音量旋钮,决定了输出信号的“推力”或“力度”。而ZQ校准则像一个专业的音响系统校准程序,它能根据现场环境(温度、电压)的变化,自动调整每个扬声器的音量和音色,确保无论处于音乐厅还是露天场地,播放效果都清晰精准、不失真。

注意:目前DataSheet在配置驱动强度和ZQ校准上没有明确先后顺序要求,但是在高速流程图里,是先设置驱动强度再去配置ZQ校准。

DCC Training

NAND Flash 中的 DCC Training(Duty Cycle Correction Training,占空比校正训练)是一项用于提升高速NAND接口数据传输可靠性的关键技术。它主要用于校准信号RE_t/c的占空比,以提供最佳的数据采样窗口。

FW可以发出以下两种时序,查询SR[0]的结果来确认当前RE_t/c是否能够正常使用。如果SR[0] == 1,需要调整占空比后,重新发起。

DCC Training 的两种方式

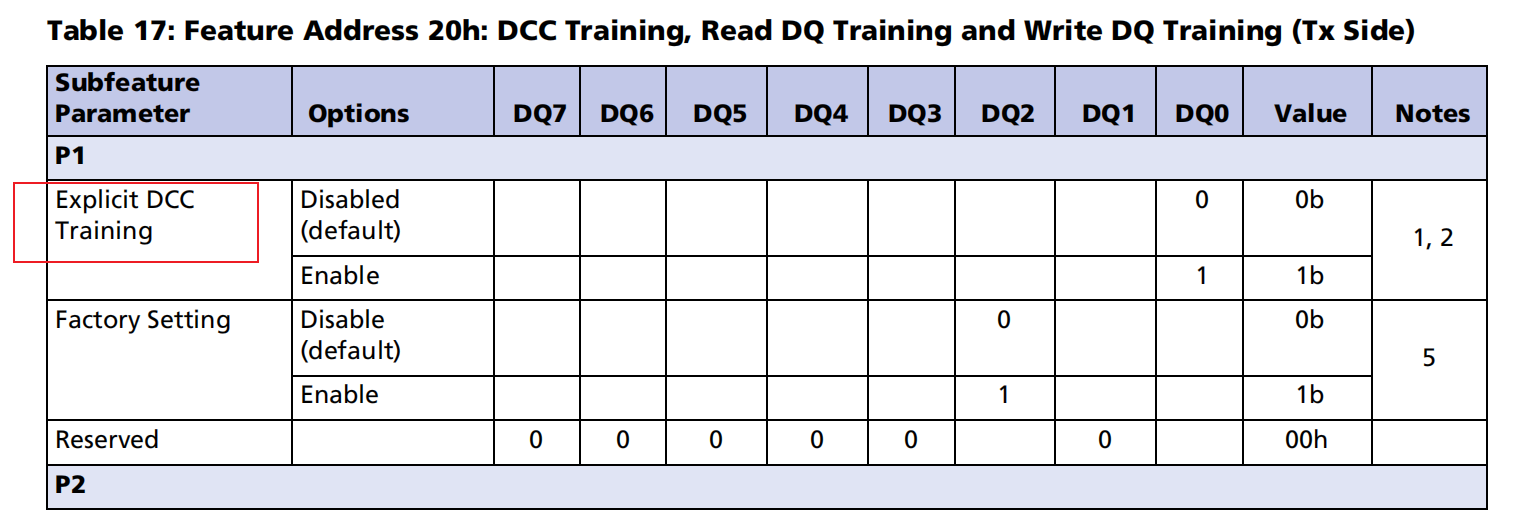

DCC Training Using Set Feature

- 开始DCC Training 前,Set Feature 20h P1[0]设置为1,将DCCE_EN使能

- 发起Random out时序,不需要处理返回的数据。Nand 在RE Toggle阶段,内部RE时钟正在进行校准

- 通过Read Status命令查看SR[0]进行check。若fail,主控需要调整REDCC相关配置,重新发起Random out进行校准

- 完成DCC Training后,需要将DCCE_EN Disable

DCC Training by using Command

- 18h后读取的长度为完整的page size

- 不需要处理返回的数据

- 通过Read Status命令查看SR[0]进行check。若fail,Nand先发起Reset(FFh)完成后,主控再调整REDCC相关配置,重新进行校准

DQ Training

Read/Write Training 的核心目的是通过校准DQ(数据)与 DQS(数据选通)的时序偏移、NAND / 主机的内部参考电压(VrefQ),确保高速读写时数据采样准确,仅适用于 NV-DDR3 和 NV-LPDDR4 接口。

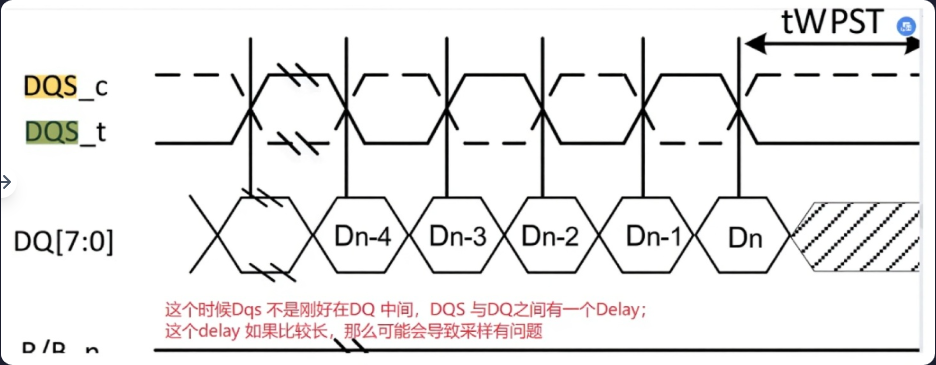

如上图可见,FW读取数据时,DQS的边沿并不是恰好指向DQ中间,两者可能会有一个gap(专业术语叫相位偏移Skew)。如果gap比较大,且FW没有采取任何措施的话,那么可能会造成采样出错。

由于FW无法改变Nand发出的时序,因此FW需要通过不断地进行read data训练,寻找一定规律,确认Nand发出的DQ和DQS之间的gap大致是多少,并调整FW接收端的DQ和DQS的delay。

当前常见确认delay的方法是:找到左右边界然后取中间值。

Read DQ Training

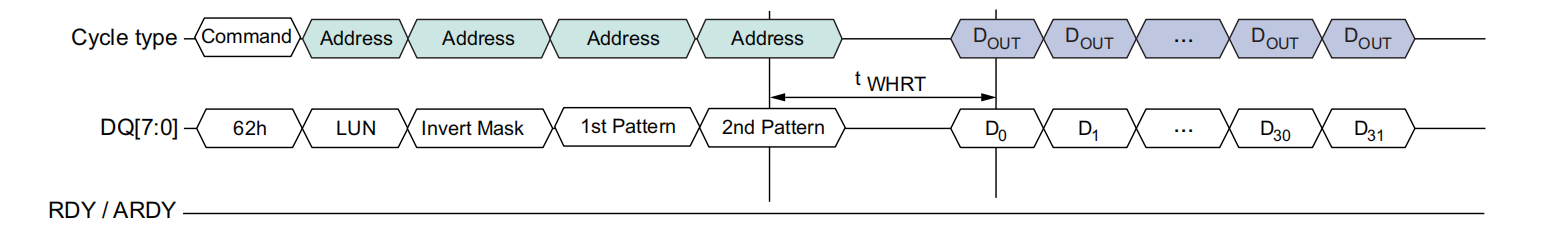

Read DQ Training是Nand输出16Byte用户自定义Pattern DQ数据的功能(一些厂商可能提供32Byte)。主控侧通过调节RDQ与RDQS的相位/延迟,确保可以正确读取Nand侧的数据。

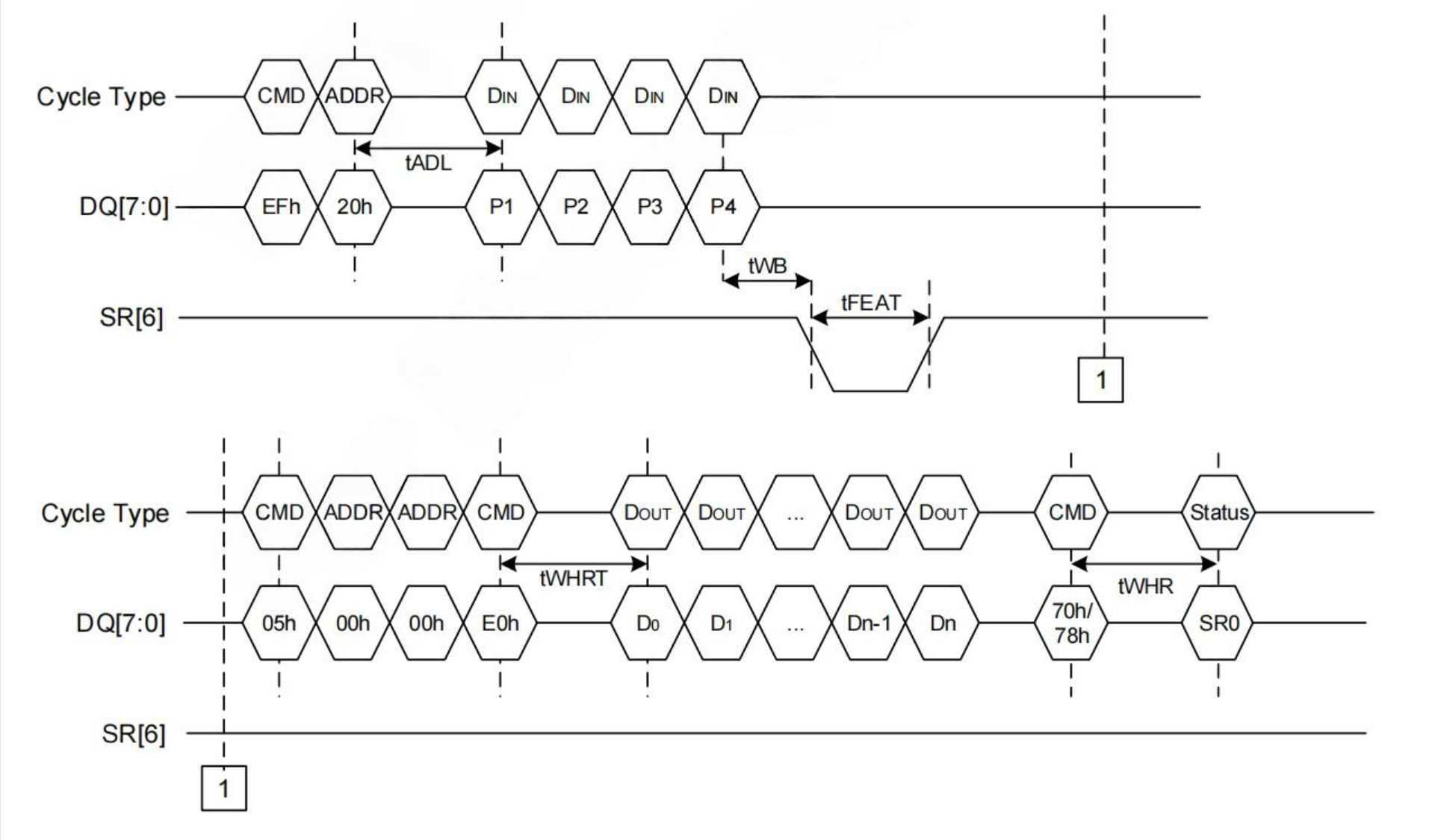

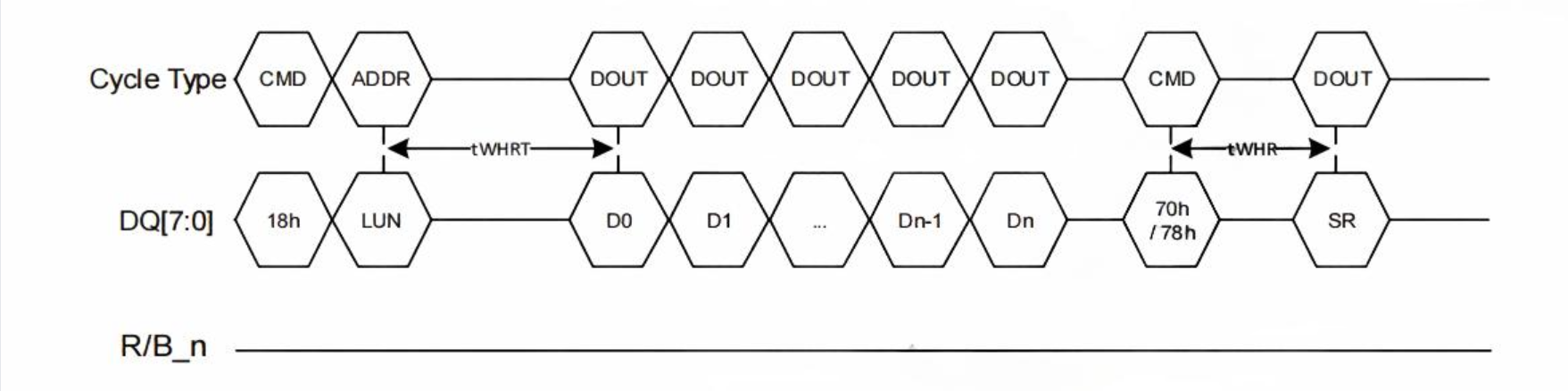

相关时序如下:

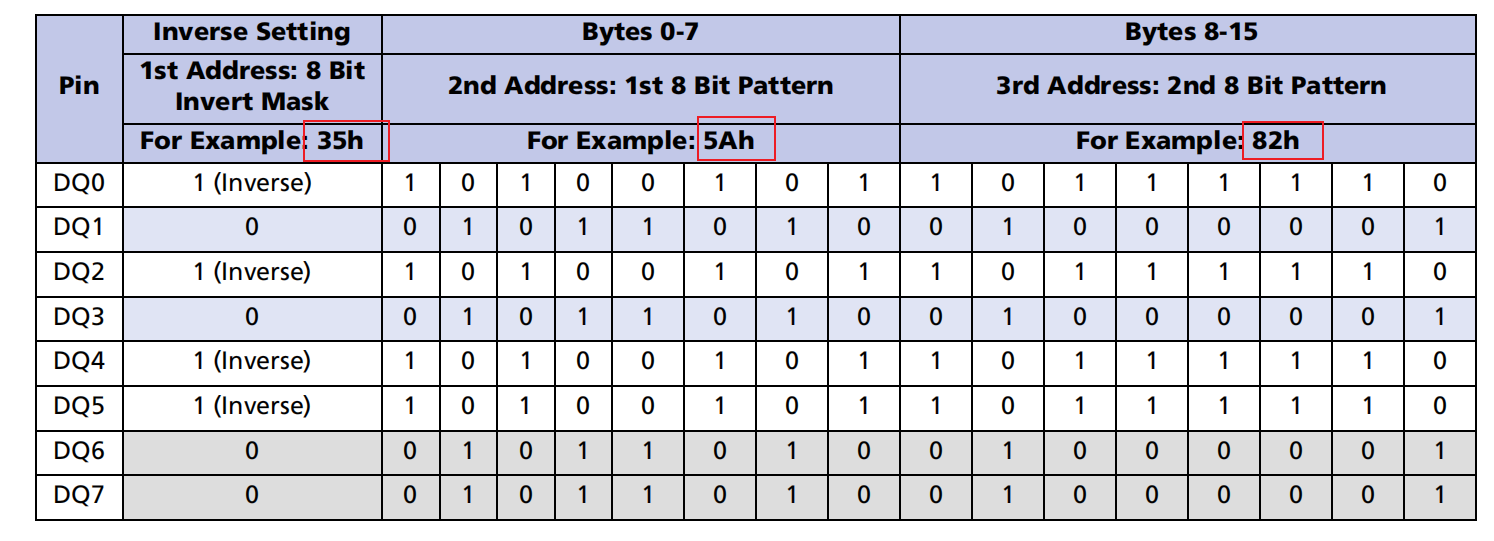

Nand反馈的数据是一个相对固定的值,具体数据由发出去的ADDR决定(Inverse Set/ 1st Pattern/ 2nd Pattern)。

以下为官方提供的一个Inverse Set = 0x35; 1st pattern = 0x5A;2nd pattern = 0x82时,FW发送62h nand吐出的数据内容:

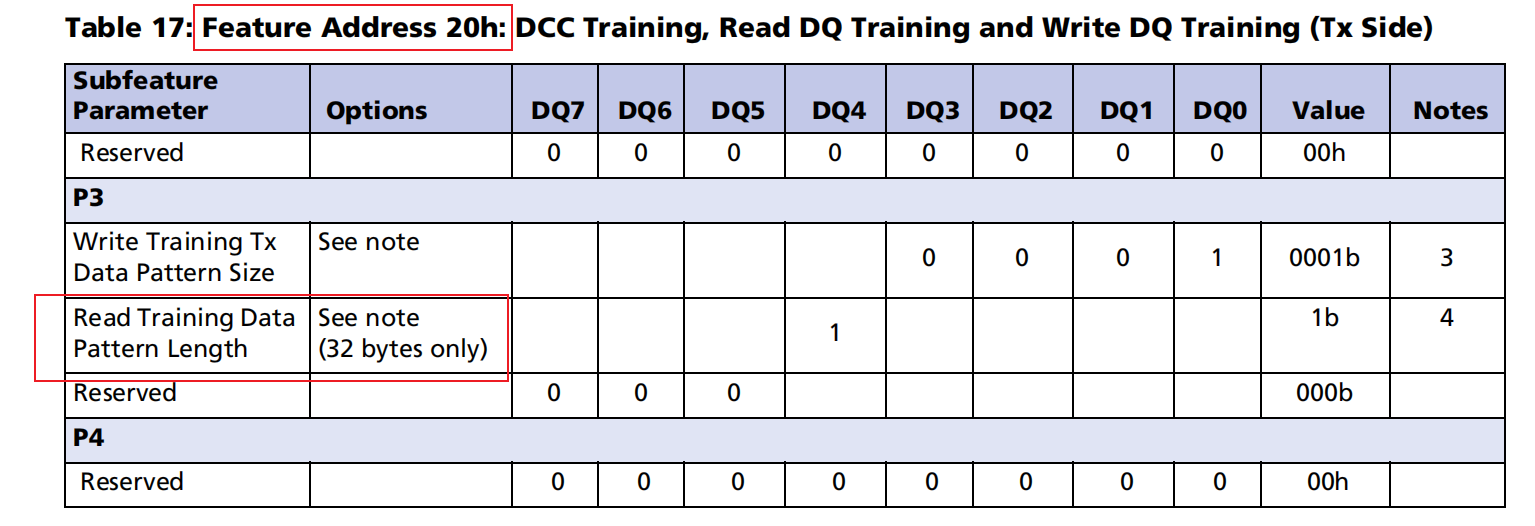

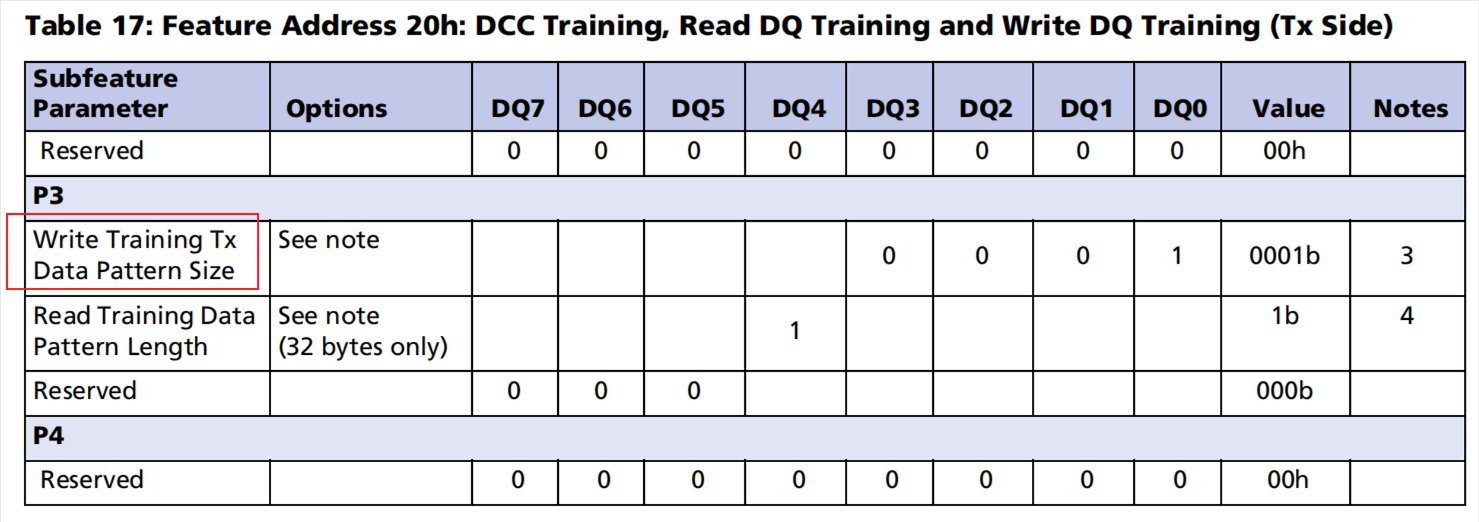

需要注意的是,Nand吐出16Byte还是32byte的数据,可以通过set feature FA 20h P3来决定(有些介质固定)。

Write DQ Training

Write DQ Training与Read DQ Training一样,DQS与DQ存在Gap。与之不同的是,Write Training是为了纠正主控发送给Nand端的DQS与DQ之间的Gap。

Write DQ Training是通过Nand的写+读来确定写入的数据是否正常,主控侧通过调节WDQ与WDQS的相位/延迟,确保可以写入数据成功。

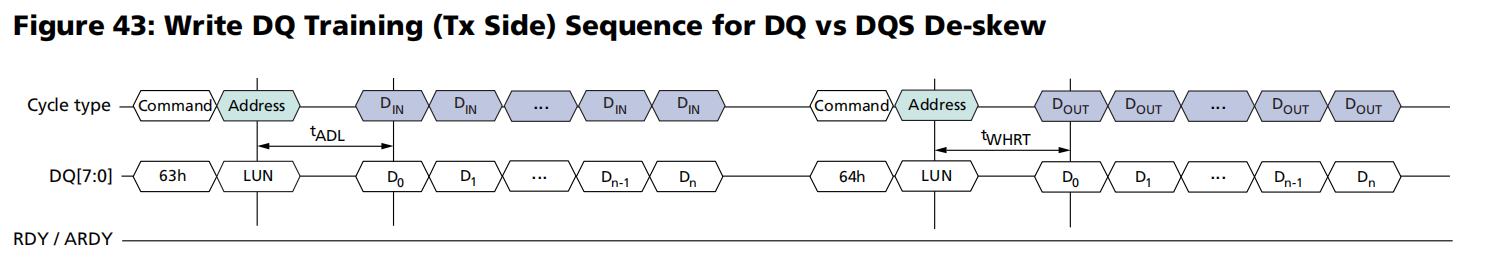

参考时序如下:

- 63h CMD用于Host发送数据给Nand。

- 64h CMD用于Host读取写入到Nand的数据。

Write Training Data size由Nand预先定义,可通过Get Feature Addr 20h P3[3:0]进行获取

FW是通过读取写入的数据是否与预期一致来判断Write DQ training是否通过。

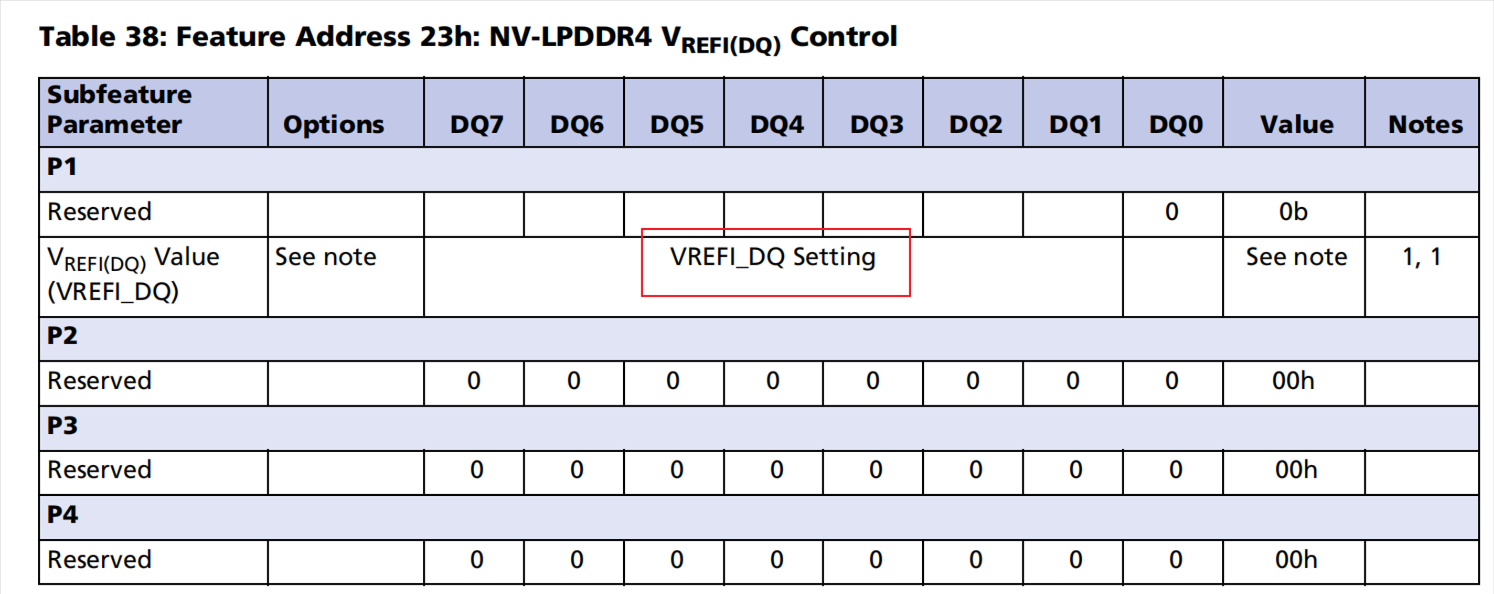

Internal VrefQ Training(DDR4 Only)

在NV-LPDDR4模式下,NAND内部VREFQ校准是提升高速信号完整性的必要条件。通过写入DQ训练中的连续读写操作配合内部VREFQ校准,可实现对VREFQ的精准校准。

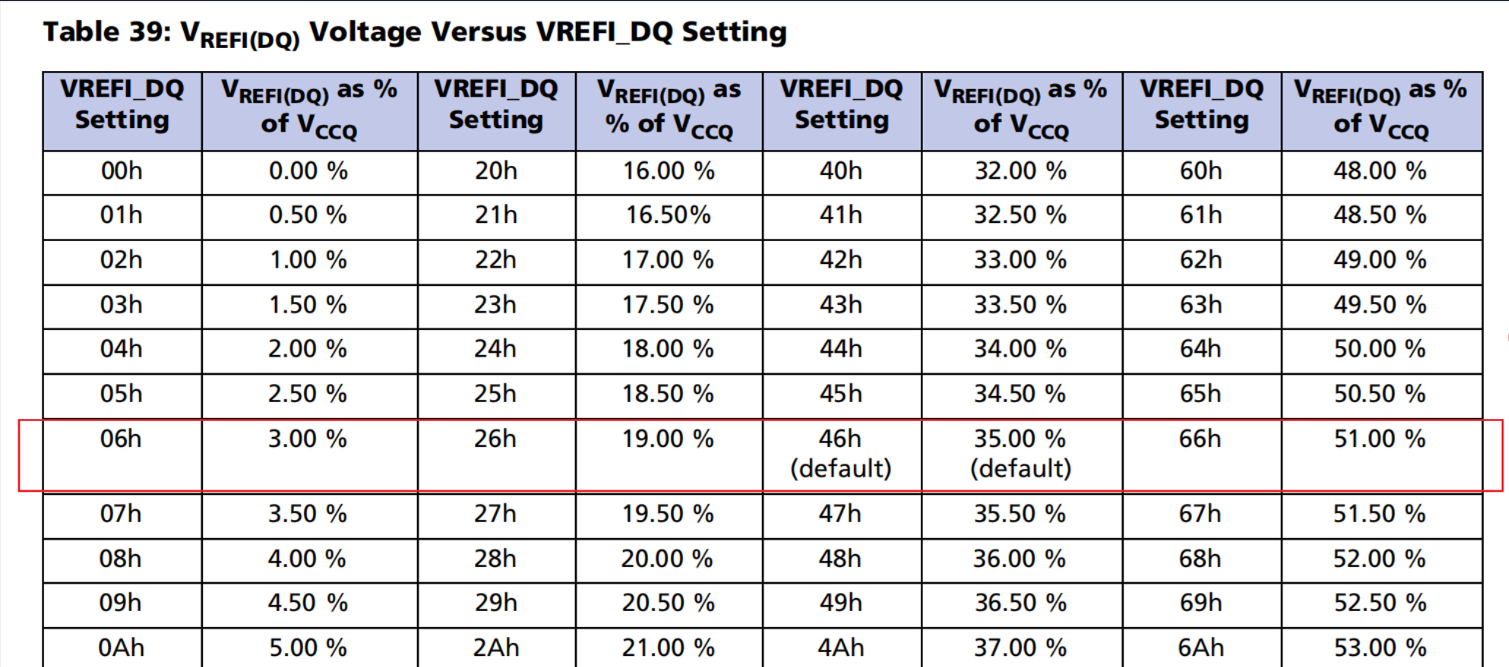

Internal VrefQ Training是通过遍历设定值,找左右边界取中间得到一个比较合适的Vref。

Internal VrefQ Training需要通过Write Training配合进行,找到最佳Vref配置。